NVIDIA’s Blackwell GPUs are expensive to produce, primarily due to larger memory footprints and more advanced packaging. Based on our bill of materials model, we estimate that the NVIDIA B200 costs $5,700 - $7,300 to produce, with HBM memory and advanced packaging together accounting for roughly two-thirds of the total unit cost. These estimates reflect only variable costs and exclude fixed costs such as R&D.

Reports suggest a sale price of $30,000 to $40,000 per chip, which implies a chip-level gross margin of around 82% for NVIDIA. Since most Blackwell revenue comes from servers and rack-scale systems, which may carry lower margins, NVIDIA’s realized margins on Blackwell sales may be lower than these chip-level estimates.

Epoch's work is free to use, distribute, and reproduce provided the source and authors are credited under the Creative Commons BY license.

Learn more about this graph

We estimate the manufacturing cost of NVIDIA’s B200 GPU by modeling the cost for logic die fabrication, high-bandwidth memory (HBM), advanced packaging, associated packaging yield losses, and auxiliary module components. The goal of this analysis is to approximate the accelerator-module production cost, not the cost of full servers or rack-scale systems.

Data

Our cost inputs are drawn from public reporting, analyst cost estimates of sub-components, teardown-based pricing estimates, company disclosures, and capacity and revenue disclosures from TSMC. Given that many of the relevant quantities are not publicly reported as exact values—such as Blackwell packaging costs, die yields, and contract HBM pricing—we model these as probability distributions within plausible ranges rather than as single-point estimates.

-

Logic die fabrication: The B200 uses two ~800 mm² compute chiplets fabricated on TSMC’s 4NP process. We estimate that a 12-inch wafer at the 4NP process node costs $17,000. Die yield is modeled as a triangular distribution between 40% and 70% and centered at 60%, based on the range of yields for high-area chiplets on comparable process nodes.

-

HBM memory: The B200 integrates 192 GB of HBM3E, which we price using a triangular distribution from $14 to $17 per GB, centered at $15.

-

Advanced packaging: Rather than assigning a component-level packaging price directly, we estimate packaging cost using a top-down revenue allocation approach. We start with the share of TSMC revenue held by advanced packaging, allocate the portion likely corresponding to CoWoS, adjust for NVIDIA’s share of CoWoS capacity, and then distribute this total packaging spend across projected Blackwell units. We model uncertainty in:

- CoWoS share of advanced packaging revenue (70 - 85%)

- NVIDIA share of CoWoS capacity (63 - 70%)

- Total Blackwell unit shipments (4.5 - 5.0 million units), and

- The Blackwell Ultra packaging cost premium (25 - 40%)

-

Packaging yield loss: We model the yield of the CoWoS-L packaging process as between 65% and 95%. When a package fails testing, the logic dies and HBM stacks integrated into that package cannot be recovered. We apply this yield adjustment only to the die and HBM cost components, dividing their base costs by the packaging yield, to reflect the effective cost per good unit. We don’t apply this yield adjustment to packaging cost itself, since our top-down revenue allocation already divides total TSMC packaging revenue by the number of good packages shipped (i.e., yield losses are implicitly captured). We also don’t apply the adjustment to auxiliary components, which are mounted to modules only after they pass final package testing.

-

Auxiliary components: power delivery hardware, PCB, and module-level assembly and testing.

Analysis

We calculate the cost of a single B200 module by sampling all uncertain parameters via a Monte Carlo simulation which can be found here. The final per-unit B200 cost is the sum of logic die cost, HBM cost, packaging cost, associated yield losses, and auxiliary module cost.

Detailed notes of the analysis can be found here.

Assumptions and limitations

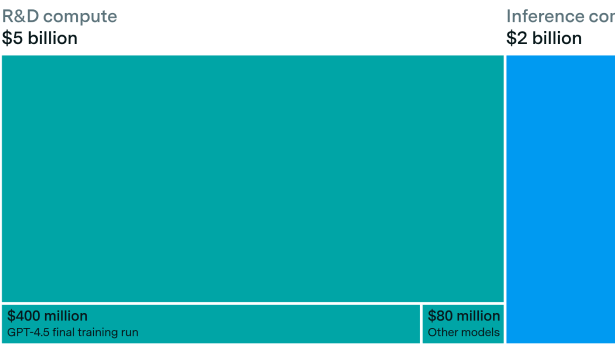

This analysis estimates manufacturing cost, not NVIDIA’s total cost structure. It does not include R&D amortization, software integration, network fabric, data center infrastructure, NVIDIA sales margins, or other services. HBM pricing is negotiated individually and can vary significantly by volume and contract length.

The advanced packaging cost estimate requires several assumptions:

- While there are public reports indicating the share of TSMC’s CoWoS capacity allocated to NVIDIA, there are no public disclosures or estimates of the share of CoWoS or advanced packaging revenue attributable to NVIDIA. This distinction matters because CoWoS capacity is measured in wafer starts, whereas CoWoS revenue also depends on the cost per wafer, which could vary across customers and products.

- The per-wafer cost depends on factors such as interposer area, number of HBM stacks, stack height, TSV configuration, substrate routing density, final package yield, and additional assembly or burn-in test steps. As a result, 70% of CoWoS wafer capacity does not necessarily imply 70% of CoWoS revenue. To account for this, we model the mapping from capacity share to revenue share as a multiplier (1.0–1.3x).

- Since Blackwell packages use large interposers, large logic dies, and high HBM stack counts, we assume they are among the more complex and higher-cost CoWoS processes. For this reason, we do not assume that NVIDIA’s revenue share could be lower than its wafer capacity share (i.e. we do not consider multipliers below 1.0x). Instead, we model the mapping from capacity share to revenue share as a multiplier from 1.0x to 1.3x, reflecting the likelihood that NVIDIA’s CoWoS packages are at least average complexity and likely above average in cost per wafer.

Our cost estimates apply at the chip-module level. Most Blackwell revenue comes from integrated subsystems, such as GB200 compute trays and HGX boards, sold to OEMs/ODMs likely at lower margins. Thus, NVIDIA’s realized gross margins are likely lower than the chip-level margins implied here.